- 您现在的位置:买卖IC网 > Sheet目录3873 > PIC16F887-I/P (Microchip Technology)IC PIC MCU FLASH 8KX14 40DIP

PIC16F88X

DS80302F-page 10

2009 Microchip Technology Inc.

8.

Module: Asynchronous Timer1

This Errata supersedes Errata DS80233 and

DS80329.

When TImer1 is started or updated, the timer

needs to see a falling edge from the external clock

source before a rising edge can increment the

counter. If writes to TMR1H and TMR1L are not

completed while the external clock pulse is still

high, Timer1 will not count the first clock pulse

after the update.

When using an external crystal, the pulse width

from

rising

to

falling

edge

is

temperature

dependent and may decrease with temperature.

As a result, the timer may require an additional

oscillation to overflow.

Work around

Switching to the HFINTOSC after reloading, the

timer ensures the Timer1 will see a falling edge

before switching back to the external clock source.

Due to the time from Timer1 overflow to the reload

being application specific, wait for the timer to

increment before beginning the reload sequence.

This ensures the timer does not miss a rising edge

during reload.

EXAMPLE 3:

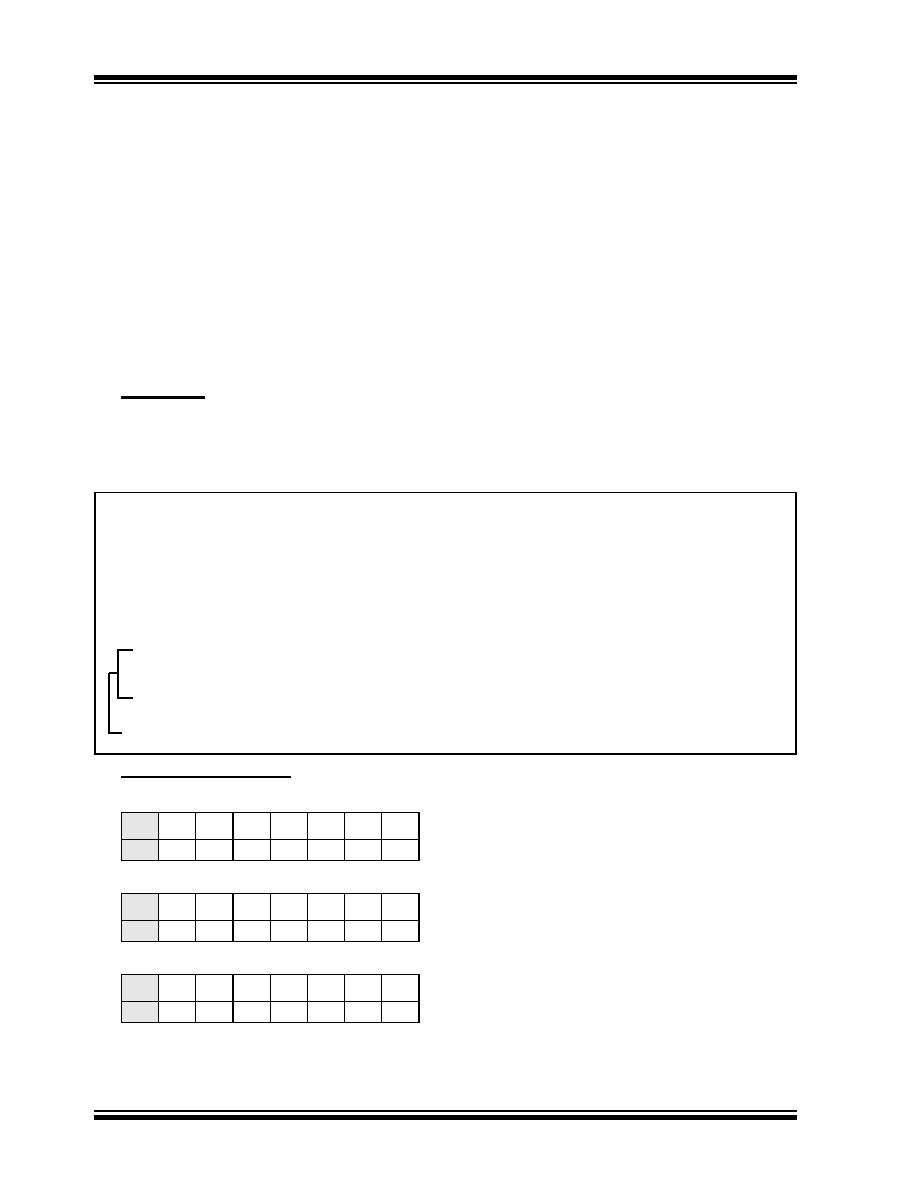

Affected Silicon Revisions

PIC16F882

PIC16F883/PIC16F884

PIC16F886/PIC16F887

BTFSC

TMR1L,0

GOTO

$-1

BTFSS

TMR1L,0

GOTO

$-1

;Timer has just incremented, 31

μs before next rising edge to

;complete reload

Update:

BCF

T1CON,TMR1CS

;Select HFINTOSC for Timer1

BSF

TMR1H,7

;Timer1 high byte 0x80

BCF

T1CON,TMR1ON

;Timer1 off

BSF

T1CON,TMR1CS

;Select external crystal

BCF

T1CON,TMR1ON

;Timer1 on

Critical Timing of code sequence for instructions following last write to TMR1L or TMR1H.

A0

X

A0

X

A2

X

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16CR76-I/SP

IC PIC MCU 8KX14 28DIP

PIC16CR76-I/SO

IC PIC MCU 8KX14 28SOIC

PIC16CR76-I/ML

IC PIC MCU 8KX14 28QFN

PIC16CR74T-I/ML

IC PIC MCU 4KX14 44QFN

PIC16CR74-I/PT

IC PIC MCU 4KX14 44TQFP

PIC16CR74-I/P

IC PIC MCU 4KX14 40DIP

PIC16CR74-I/ML

IC PIC MCU 4KX14 44QFN

PIC16CR73T-I/SS

IC PIC MCU 4KX14 28SSOP

相关代理商/技术参数

PIC16F887-I/PT

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F887T-I/ML

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F887T-I/PT

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F88-E/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F88-E/P

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F88-E/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F88-E/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F88-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT